«دیکدرهای باینری» (Binary Decoders) دستهای از مدارهای منطقی ترکیبی هستند که در ساخت آنها از گیتهای منطقی پایه استفاده شده و عملکرد آنها دقیقاً عکس انکدرهاست.

سرویس آموزش و آزمون برق نیوز،«دیکدرهای باینری» (Binary Decoders) دستهای از مدارهای منطقی ترکیبی هستند که در ساخت آنها از گیتهای منطقی پایه استفاده شده و عملکرد آنها دقیقاً عکس انکدرهاست.

کلمهی Decoder به معنای ترجمه یا رمزگشایی اطلاعات رمزنگاری شده از یک قالب به قالبی دیگر است؛ لذا یک دیکدر دیجیتالی، دستهای از سیگنالهای دیجیتال را از ورودی گرفته و به یک کد دهدهی معادل تبدیل میکند.

دیکدرهای باینری گونهای از ادوات منطق دیجیتالی هستند که بسته به تعداد خطوط دادهی ورودی ممکن است در ورودیشان کدهای ۲ بیتی، ۳ بیتی، ۴ بیتی و … میپذیرند. به طور کلی دیکدر یک کد n. بیتی در ورودی را گرفته و به حداکثر ۲n خط خروجی منحصر به فرد در خروجی تبدیل میکند، همچنین دیکدرها مشخصاً با ۱ کردن تنها یکی از مثلاً n. بیت خروجی، یک مقدار باینری در ورودی را به یک مقدار غیر باینری در خروجی تبدیل میکنند.

اگر یک دیکدر باینری n. ورودی دریافت کند (که معمولاً به عنوان یک عدد باینری یا بولی کنار هم قرار میگیرند)، بر اساس آن ورودی تنها و تنها یکی از ۲n خروجی خود را فعال کرده و سایر پایههای خروجی را غیرفعال میکند.

یک معکوس کننده (گیت NOT) را میتوان به عنوان نوعی دیکدر باینری ۱ به ۲ در نظر گرفت، زیرا با ۱ ورودی A. امکان تولید ۲۱ خروجی A. و A’ وجود دارد.

البته اگر کد n. بیتی ورودی دارای ترکیبات بلااستفاده باشد، دیکدر ممکن است خروجیهایی کمتر از ۲n تا داشته باشد. اینگونه دیکدرها را دیکدرهای n. به m. مینامند که m. ≤ ۲n است. خروجی (Q) این دیکدرها همانند سایر مدارهای منطقی ترکیبی تنها به وضعیت فعلی ورودیها وابسته است. به عبارت سادهتر، دیکدر باینری به ورودیهای فعلی خود نگاه کرده و میفهمد چه کد باینری یا عدد باینری در حال حاضر بر روی ورودی وجود دارد، و سپس خروجی متناسب با این ورودی باینری را انتخاب میکند.

همانگونه که اشاره شد، دیکدر ورودیهای کدگذاری شده را به خروجیهای کدگذاری شده تبدیل میکند که کدهای ورودی و خروجی از جنس متفاوتند. دیکدرها را میتوان برای کدگشایی و تبدیل ورودیهای باینری یا BCD به یک دهدهی خروجی استفاده کرد. رایجترین دیکدرهای BCD به دهدهی عبارتند از: TTL ۷۴۴۲ و CMOS ۴۰۲۸. معمولاً کد خروجی دیکدرها تعداد بیتهای بیشتری نسبت به کد ورودی آن دارد. کاربردیترین مدارهای دیکدر عبارتند از: طراحیهای ۲ به ۴، ۳ به ۸ و ۴ به ۱۶.

دیکدر باینری ۲ به ۴

دیکدر باینری ۷۴LS۱۳۸

تا بدین جای کار دیدیم که یک دیکدر باینری ۲ به ۴ (مثلاً TTL ۷۴۱۵۵) را میتوان برای کدگشایی هر کد باینری ۲ بیتی دلخواه استفاده کرد که در این صورت متناسب با ترکیبهای ممکن ورودیها، ۴ خروجی خواهیم داشت. هرچند که گاهی اوقات ممکن است تعداد خروجیهای موجود از تعداد خروجیهای مورد نیاز کمتر باشد، که در اینگونه مواقع با افزودن مثلاً n. پایهی ورودی، دیکدر توانایی تولید ۲n خروجی بیشتر را خواهد داشت.

به عنوان مثال TTL ۷۴۱۳۸ دیکدری با ۳ ورودی باینری (n = ۳) و ۸ خروجی است؛ TTL ۷۴۱۵۴ نیز دیکدری با ۴ ورودی باینری (n = ۴) و ۱۶ خروجی است. اما ممکن است دیکدری کمتر از ۲n تا خروجی داشته باشد، همانند TTL ۷۴۴۷ که یک دیکدر BCD به سونسگمنت است. این آیسی اگرچه ۴ ورودی دارد، اما به جای ۱۶ خروجی (۲۴) تنها ۷ پایهی خروجی فعال برای راهاندازی یک نمایشگر دارد.

شکل زیر نحوهی پیادهسازی یک دیکدر ۴ به ۱۶ را با استفاده از دو دیکدر ۳ به ۸ نشان میدهد. این ۴ پایهی ورودی از ۳ پایهی داده و ۱ پایهی فعالساز تشکیل شدهاند.

پیکربندی یک دیکدر باینری ۴ به ۱۶

ورودیهای B.، A. و C. برای انتخاب خروجی در هر یک از دیکدرها به کار میروند که خروجی انتخاب شده توسط این پایهها ۱ منطقی (HIGH) خواهد شد. ورودی D. نیز به پایههای Enable دیکدرهای ۳ به ۸ متصل شده است که مشخص میکند کدام «۱» (از دیکدر اولی یا دومی) در خروجی قرار میگیرد.

البته باید توجه داشت در تعداد ورودیهای استفاده شده برای یک دیکدر خاص محدودیت وجود دارد. زیرا هرچقدر n. افزایش یابد، تعداد گیتهای AND استفاده شده نیز افزایش خواهد یافت که در این صورت fan-out لازم برای راهاندازی گیتها نیز بسیار بزرگ خواهد بود.

دیکدرهایی که در مثالهای قبل دیدیم همه از نوع فعالبالا یا اَکتیو-های (active-HIGH) بودند؛ یعنی تنها در صورتی خروجی اعمال میشود که پایهی Enable آیسی ۱ شود. این دیکدرها را میتوان تنها با استفاده از گیتهای NOT و AND پیادهسازی کرد. گیت AND به عنوان عنصر پایهی کدگشایی به شمار میرود چرا که تنها زمانی خروجیاش ۱ میشود که تمام ورودیهای آن ۱ باشند.

در ساختار گروهی دیگر از دیکدرها به جای گیتهای AND از گیتهای NAND استفاده میشود. علت این کار به قیمت ارزانتر گیتهای NAND نسبت به گیتهای AND برمیگردد، چرا که در ساختار گیت NAND از تعداد ترانزیستور کمتری استفاده میشود.

دیکدر ۲ به ۴ با استفاده از گیت NAND

خروجیهای دیکدر NAND برعکس دیکدرهای قبلی است؛ یعنی تنها یک پایهی خروجی LOW یا ۰ منطقی بوده و سایر پایهها HIGH یا ۱ منطقی هستند.

دیکدرهای NAND نیز ممکن است پایهی Enable داشته باشند که در این صورت با ۰ و ۱ کردن پایهی فعالساز میتوان روشن یا خاموش بودن خروجی را کنترل کرد. در دیکدری که با گیت NAND ساخته شده است، در صورت LOW شدن پایهی فعالساز (EN = ۰) بدون توجه به مقدار ورودیهای A. و B. تمام خروجیها خاموش یا ۱ منطقی خواهند شد.

اگر بخواهیم مدارهای قبلی ساخته شده با گیتهای AND یا NAND را بهگونهای تغییر دهیم که پایهی فعالساز نیز داشته باشند، تنها کافی است بهجای گیتهای AND یا NAND با ۲ پایهی ورودی، گیتهایی با ۳ پایهی ورودی قرار دهیم. پایههای ورودی اضافه شده را به هم متصل کرده و به عنوان پایهی Enable استفاده میکنیم.

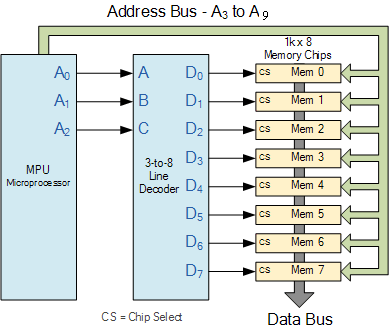

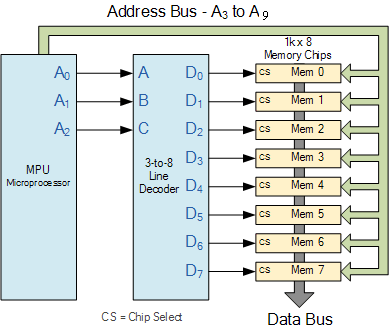

دیکدر آدرس حافظه

در سیستمهای میکروپروسسوری و دیجیتالی پیچیده عموماً برای دسترسی به خانهی مشخصی از حافظه که آدرس آن مشخص است، از دیکدرهای باینری استفاده میکنند. مقدار حافظهی لازم برای اینگونه سیستمها بسیار زیاد است و لذا استفاده از تنها یک تراشهی حافظه کافی نخواهد بود.

یکی از روشهای غلبه بر این مشکل اتصال چندین تراشهی حافظه به یکدیگر و خواندن و نوشتن دادهها از طریق یک «باس دادهی مشترک» (common Data Bus) است. در هر لحظه از زمان تنها یکی از تراشههای حافظه انتخاب شده و اطلاعات از روی آن خوانده میشود که به این فرآیند «کدگشایی آدرس» یا آدرس دیکدینگ (Address Decoding) گفته میشود.

در این روش، آدرسی که گرفته میشود همان دادهی ورودی کدگذاری شده است. خروجیها نیز سیگنالهای انتخاب عنصری از حافظه هستند. هر تراشهی حافظه یک پایهی ورودی به نام «انتخاب تراشه» یا Chip Select) CS) دارد که واحد میکروپروسسوری یا micro-processor unit) MPU) از طریق این پایه تراشهی حافظهی مناسب را انتخاب میکند. عموماً پایههای CS فعالبالا هستند، یعنی ۱ بودن این پایه باعث انتخاب تراشهی حافظه میشود؛ لذا میتوان با انتخاب یا عدم انتخاب هر یک از تراشهها در هر لحظه از زمان آدرس حافظهی مناسب را برگزید. مزیت آدرس دیکدینگ در این است که به ازای هر آدرس حافظهی مشخص، تنها یک خانهی حافظه در یکی از تراشهها وجود خواهد داشت.

به عنوان مثال فرض میکنیم یک میکروپروسسور ساده ۱Kb حافظهی RAM و ۱۰ خط آدرس دارد. در این سیستم حافظهی RAM از ۸ تراشه که هرکدام ۱۲۸ خانهی حافظه دارند تشکیل شده است و هر خانهی حافظه ۸ بیتی است. مطابق شکل زیر برای انتخاب صحیح هر کدام از تراشههای حافظه به یک دیکدر ۳ به ۸ نیاز خواهیم داشت.

دیکدینگ آدرس حافظه

دیکدر باینری برای انتخاب هر کدام از ۸ تراشه تنها به ۳ خط آدرس (A۰ تا A۲) احتیاج دارد (بخش کم ارزشتر آدرس)؛ ۷ خط آدرس باقیمانده (A۳ تا A۹) نیز برای انتخاب یک خانهی حافظه در تراشهی انتخاب شده به کار میروند.

پس از انتخاب یک خانهی حافظه از طریق باس آدرس، اطلاعات این خانه به باس دادهی مشترک ارسال میشود تا مورد استفادهی میکروپروسسور قرار گیرد. هر چند که مثال بررسی شده در بالا بسیار ساده بود، اما همین اصول برای سایر تراشههای حافظه نیز پابرجاست.

استفاده از دیکدرهای باینری برای تبدیل فرمتهای دیجیتالی به یکدیگر، مثل تبدیل دادههای نوع باینری یا BCD به دهدهی و اُکتال بسیار سودمند است. پرکاربردترین آیسیهای دیکدر عبارتند از: دیکدر ۳ به ۸ TTL ۷۴LS۱۳۸ و دیکدر ۴ به ۱۶، ۷۴ALS۱۵۴. ضمناً آیسیهای دیکدری مثل TTL ۷۴LS۴۷ نیز وجود دارند که به عنوان رابط نمایشگرهای سونسگمنت (Seven-Segment) به کار میروند. در بخش بعدی از مجموعه آموزشهای مربوط به مدارهای منطقی ترکیبی راجع به این نوع دیکدرها صحبت خواهیم کرد.

کلمهی Decoder به معنای ترجمه یا رمزگشایی اطلاعات رمزنگاری شده از یک قالب به قالبی دیگر است؛ لذا یک دیکدر دیجیتالی، دستهای از سیگنالهای دیجیتال را از ورودی گرفته و به یک کد دهدهی معادل تبدیل میکند.

دیکدرهای باینری گونهای از ادوات منطق دیجیتالی هستند که بسته به تعداد خطوط دادهی ورودی ممکن است در ورودیشان کدهای ۲ بیتی، ۳ بیتی، ۴ بیتی و … میپذیرند. به طور کلی دیکدر یک کد n. بیتی در ورودی را گرفته و به حداکثر ۲n خط خروجی منحصر به فرد در خروجی تبدیل میکند، همچنین دیکدرها مشخصاً با ۱ کردن تنها یکی از مثلاً n. بیت خروجی، یک مقدار باینری در ورودی را به یک مقدار غیر باینری در خروجی تبدیل میکنند.

اگر یک دیکدر باینری n. ورودی دریافت کند (که معمولاً به عنوان یک عدد باینری یا بولی کنار هم قرار میگیرند)، بر اساس آن ورودی تنها و تنها یکی از ۲n خروجی خود را فعال کرده و سایر پایههای خروجی را غیرفعال میکند.

یک معکوس کننده (گیت NOT) را میتوان به عنوان نوعی دیکدر باینری ۱ به ۲ در نظر گرفت، زیرا با ۱ ورودی A. امکان تولید ۲۱ خروجی A. و A’ وجود دارد.

البته اگر کد n. بیتی ورودی دارای ترکیبات بلااستفاده باشد، دیکدر ممکن است خروجیهایی کمتر از ۲n تا داشته باشد. اینگونه دیکدرها را دیکدرهای n. به m. مینامند که m. ≤ ۲n است. خروجی (Q) این دیکدرها همانند سایر مدارهای منطقی ترکیبی تنها به وضعیت فعلی ورودیها وابسته است. به عبارت سادهتر، دیکدر باینری به ورودیهای فعلی خود نگاه کرده و میفهمد چه کد باینری یا عدد باینری در حال حاضر بر روی ورودی وجود دارد، و سپس خروجی متناسب با این ورودی باینری را انتخاب میکند.

همانگونه که اشاره شد، دیکدر ورودیهای کدگذاری شده را به خروجیهای کدگذاری شده تبدیل میکند که کدهای ورودی و خروجی از جنس متفاوتند. دیکدرها را میتوان برای کدگشایی و تبدیل ورودیهای باینری یا BCD به یک دهدهی خروجی استفاده کرد. رایجترین دیکدرهای BCD به دهدهی عبارتند از: TTL ۷۴۴۲ و CMOS ۴۰۲۸. معمولاً کد خروجی دیکدرها تعداد بیتهای بیشتری نسبت به کد ورودی آن دارد. کاربردیترین مدارهای دیکدر عبارتند از: طراحیهای ۲ به ۴، ۳ به ۸ و ۴ به ۱۶.

دیکدر باینری ۲ به ۴

در مثال سادهی بالا برای ساخت یک دیکدر ۲ به ۴ از چهار گیت AND استفاده شده است. ۲ ورودی باینری که با A. و B. مشخص شدهاند کدگشایی شده و به ۴ خروجی متصل میشوند، که این طرز عملکرد همان تعریف دیکدر است. هر یک از خروجیها نمایشگر یکی از مینترمهای متعلق به ۲ ورودی است.

ورودیهای باینری A. و B. مشخص میکنند که کدام یک از خطوط خروجی Q۰ تا Q۳ یک منطقی یا HIGH است که در این صورت بقیهی پایهها همگی صفر منطقی یا LOW میشوند؛ لذا HIGH بودن هر خط خروجی نشاندهندهی کد باینری است که در ورودی وجود دارد.

برخی از دیکدرهای باینری یک پایهی ورودی دیگر نیز دارند که پایهی فعالساز (Enable) نامیده میشود. این پایه وظیفهی کنترل خروجی قطعه را بر عهده دارد. با به کارگیری پایهی فعالساز میتوان خروجی دیکدر را در مواقع لازم روشن یا خاموش کرد. معمولاً دیکدرهای دارای پایهی فعالساز به عنوان «دیکدرهای آدرس حافظه» (memory address decoders) در حافظههای میکروپروسسوری کاربرد دارند.

میتوان گفت که دیکدر باینری همان دیمالتیپلکسر با یک خط دادهی بیشتر است که این خط داده همان پایهی فعالساز دیکدر است. یک روش دیگر برای تفسیر طرز عملکرد دیکدر به این صورت است که ورودیهای B.، A. و C. را به عنوان سیگنالهای آدرس در نظر بگیریم که در این صورت هر ترکیب B.، A. و C. بیانگر یک آدرس حافظهی منحصر به فرد خواهد بود.

ورودیهای باینری A. و B. مشخص میکنند که کدام یک از خطوط خروجی Q۰ تا Q۳ یک منطقی یا HIGH است که در این صورت بقیهی پایهها همگی صفر منطقی یا LOW میشوند؛ لذا HIGH بودن هر خط خروجی نشاندهندهی کد باینری است که در ورودی وجود دارد.

برخی از دیکدرهای باینری یک پایهی ورودی دیگر نیز دارند که پایهی فعالساز (Enable) نامیده میشود. این پایه وظیفهی کنترل خروجی قطعه را بر عهده دارد. با به کارگیری پایهی فعالساز میتوان خروجی دیکدر را در مواقع لازم روشن یا خاموش کرد. معمولاً دیکدرهای دارای پایهی فعالساز به عنوان «دیکدرهای آدرس حافظه» (memory address decoders) در حافظههای میکروپروسسوری کاربرد دارند.

میتوان گفت که دیکدر باینری همان دیمالتیپلکسر با یک خط دادهی بیشتر است که این خط داده همان پایهی فعالساز دیکدر است. یک روش دیگر برای تفسیر طرز عملکرد دیکدر به این صورت است که ورودیهای B.، A. و C. را به عنوان سیگنالهای آدرس در نظر بگیریم که در این صورت هر ترکیب B.، A. و C. بیانگر یک آدرس حافظهی منحصر به فرد خواهد بود.

دیکدر باینری ۷۴LS۱۳۸

تا بدین جای کار دیدیم که یک دیکدر باینری ۲ به ۴ (مثلاً TTL ۷۴۱۵۵) را میتوان برای کدگشایی هر کد باینری ۲ بیتی دلخواه استفاده کرد که در این صورت متناسب با ترکیبهای ممکن ورودیها، ۴ خروجی خواهیم داشت. هرچند که گاهی اوقات ممکن است تعداد خروجیهای موجود از تعداد خروجیهای مورد نیاز کمتر باشد، که در اینگونه مواقع با افزودن مثلاً n. پایهی ورودی، دیکدر توانایی تولید ۲n خروجی بیشتر را خواهد داشت.

به عنوان مثال TTL ۷۴۱۳۸ دیکدری با ۳ ورودی باینری (n = ۳) و ۸ خروجی است؛ TTL ۷۴۱۵۴ نیز دیکدری با ۴ ورودی باینری (n = ۴) و ۱۶ خروجی است. اما ممکن است دیکدری کمتر از ۲n تا خروجی داشته باشد، همانند TTL ۷۴۴۷ که یک دیکدر BCD به سونسگمنت است. این آیسی اگرچه ۴ ورودی دارد، اما به جای ۱۶ خروجی (۲۴) تنها ۷ پایهی خروجی فعال برای راهاندازی یک نمایشگر دارد.

شکل زیر نحوهی پیادهسازی یک دیکدر ۴ به ۱۶ را با استفاده از دو دیکدر ۳ به ۸ نشان میدهد. این ۴ پایهی ورودی از ۳ پایهی داده و ۱ پایهی فعالساز تشکیل شدهاند.

پیکربندی یک دیکدر باینری ۴ به ۱۶

ورودیهای B.، A. و C. برای انتخاب خروجی در هر یک از دیکدرها به کار میروند که خروجی انتخاب شده توسط این پایهها ۱ منطقی (HIGH) خواهد شد. ورودی D. نیز به پایههای Enable دیکدرهای ۳ به ۸ متصل شده است که مشخص میکند کدام «۱» (از دیکدر اولی یا دومی) در خروجی قرار میگیرد.

البته باید توجه داشت در تعداد ورودیهای استفاده شده برای یک دیکدر خاص محدودیت وجود دارد. زیرا هرچقدر n. افزایش یابد، تعداد گیتهای AND استفاده شده نیز افزایش خواهد یافت که در این صورت fan-out لازم برای راهاندازی گیتها نیز بسیار بزرگ خواهد بود.

دیکدرهایی که در مثالهای قبل دیدیم همه از نوع فعالبالا یا اَکتیو-های (active-HIGH) بودند؛ یعنی تنها در صورتی خروجی اعمال میشود که پایهی Enable آیسی ۱ شود. این دیکدرها را میتوان تنها با استفاده از گیتهای NOT و AND پیادهسازی کرد. گیت AND به عنوان عنصر پایهی کدگشایی به شمار میرود چرا که تنها زمانی خروجیاش ۱ میشود که تمام ورودیهای آن ۱ باشند.

در ساختار گروهی دیگر از دیکدرها به جای گیتهای AND از گیتهای NAND استفاده میشود. علت این کار به قیمت ارزانتر گیتهای NAND نسبت به گیتهای AND برمیگردد، چرا که در ساختار گیت NAND از تعداد ترانزیستور کمتری استفاده میشود.

دیکدر ۲ به ۴ با استفاده از گیت NAND

خروجیهای دیکدر NAND برعکس دیکدرهای قبلی است؛ یعنی تنها یک پایهی خروجی LOW یا ۰ منطقی بوده و سایر پایهها HIGH یا ۱ منطقی هستند.

دیکدرهای NAND نیز ممکن است پایهی Enable داشته باشند که در این صورت با ۰ و ۱ کردن پایهی فعالساز میتوان روشن یا خاموش بودن خروجی را کنترل کرد. در دیکدری که با گیت NAND ساخته شده است، در صورت LOW شدن پایهی فعالساز (EN = ۰) بدون توجه به مقدار ورودیهای A. و B. تمام خروجیها خاموش یا ۱ منطقی خواهند شد.

اگر بخواهیم مدارهای قبلی ساخته شده با گیتهای AND یا NAND را بهگونهای تغییر دهیم که پایهی فعالساز نیز داشته باشند، تنها کافی است بهجای گیتهای AND یا NAND با ۲ پایهی ورودی، گیتهایی با ۳ پایهی ورودی قرار دهیم. پایههای ورودی اضافه شده را به هم متصل کرده و به عنوان پایهی Enable استفاده میکنیم.

دیکدر آدرس حافظه

در سیستمهای میکروپروسسوری و دیجیتالی پیچیده عموماً برای دسترسی به خانهی مشخصی از حافظه که آدرس آن مشخص است، از دیکدرهای باینری استفاده میکنند. مقدار حافظهی لازم برای اینگونه سیستمها بسیار زیاد است و لذا استفاده از تنها یک تراشهی حافظه کافی نخواهد بود.

یکی از روشهای غلبه بر این مشکل اتصال چندین تراشهی حافظه به یکدیگر و خواندن و نوشتن دادهها از طریق یک «باس دادهی مشترک» (common Data Bus) است. در هر لحظه از زمان تنها یکی از تراشههای حافظه انتخاب شده و اطلاعات از روی آن خوانده میشود که به این فرآیند «کدگشایی آدرس» یا آدرس دیکدینگ (Address Decoding) گفته میشود.

در این روش، آدرسی که گرفته میشود همان دادهی ورودی کدگذاری شده است. خروجیها نیز سیگنالهای انتخاب عنصری از حافظه هستند. هر تراشهی حافظه یک پایهی ورودی به نام «انتخاب تراشه» یا Chip Select) CS) دارد که واحد میکروپروسسوری یا micro-processor unit) MPU) از طریق این پایه تراشهی حافظهی مناسب را انتخاب میکند. عموماً پایههای CS فعالبالا هستند، یعنی ۱ بودن این پایه باعث انتخاب تراشهی حافظه میشود؛ لذا میتوان با انتخاب یا عدم انتخاب هر یک از تراشهها در هر لحظه از زمان آدرس حافظهی مناسب را برگزید. مزیت آدرس دیکدینگ در این است که به ازای هر آدرس حافظهی مشخص، تنها یک خانهی حافظه در یکی از تراشهها وجود خواهد داشت.

به عنوان مثال فرض میکنیم یک میکروپروسسور ساده ۱Kb حافظهی RAM و ۱۰ خط آدرس دارد. در این سیستم حافظهی RAM از ۸ تراشه که هرکدام ۱۲۸ خانهی حافظه دارند تشکیل شده است و هر خانهی حافظه ۸ بیتی است. مطابق شکل زیر برای انتخاب صحیح هر کدام از تراشههای حافظه به یک دیکدر ۳ به ۸ نیاز خواهیم داشت.

دیکدینگ آدرس حافظه

دیکدر باینری برای انتخاب هر کدام از ۸ تراشه تنها به ۳ خط آدرس (A۰ تا A۲) احتیاج دارد (بخش کم ارزشتر آدرس)؛ ۷ خط آدرس باقیمانده (A۳ تا A۹) نیز برای انتخاب یک خانهی حافظه در تراشهی انتخاب شده به کار میروند.

پس از انتخاب یک خانهی حافظه از طریق باس آدرس، اطلاعات این خانه به باس دادهی مشترک ارسال میشود تا مورد استفادهی میکروپروسسور قرار گیرد. هر چند که مثال بررسی شده در بالا بسیار ساده بود، اما همین اصول برای سایر تراشههای حافظه نیز پابرجاست.

استفاده از دیکدرهای باینری برای تبدیل فرمتهای دیجیتالی به یکدیگر، مثل تبدیل دادههای نوع باینری یا BCD به دهدهی و اُکتال بسیار سودمند است. پرکاربردترین آیسیهای دیکدر عبارتند از: دیکدر ۳ به ۸ TTL ۷۴LS۱۳۸ و دیکدر ۴ به ۱۶، ۷۴ALS۱۵۴. ضمناً آیسیهای دیکدری مثل TTL ۷۴LS۴۷ نیز وجود دارند که به عنوان رابط نمایشگرهای سونسگمنت (Seven-Segment) به کار میروند. در بخش بعدی از مجموعه آموزشهای مربوط به مدارهای منطقی ترکیبی راجع به این نوع دیکدرها صحبت خواهیم کرد.

لینک کوتاه

از ارسال دیدگاه های نا مرتبط با متن خبر، تکرار نظر دیگران، توهین به سایر کاربران و ارسال متن های طولانی خودداری نمایید.

لطفا نظرات بدون بی احترامی، افترا و توهین به مسئولان، اقلیت ها، قومیت ها و ... باشد و به طور کلی مغایرتی با اصول اخلاقی و قوانین کشور نداشته باشد.

در غیر این صورت، «برق نیوز» مطلب مورد نظر را رد یا بنا به تشخیص خود با ممیزی منتشر خواهد کرد.