فلیپ فلاپ D یا D-type Flip Flop نوعی اصلاح یافته از فلیپ فلاپهای ست-ریست (Set-Reset) یا SR است، اما برای جلوگیری از اینکه ورودیهای R و S هم زمان در یک سطح منطقی باشند، یک معکوسکننده (Inverter) یا گیت NOT به این نوع فلیپ فلاپ افزوده شده است.

سرویس آموزش و آزمون برق نیوز، فلیپ فلاپ D یا D-type Flip Flop نوعی اصلاح یافته از فلیپ فلاپهای ست-ریست (Set-Reset) یا SR است، اما برای جلوگیری از اینکه ورودیهای R و S هم زمان در یک سطح منطقی باشند، یک معکوسکننده (Inverter) یا گیت NOT به این نوع فلیپ فلاپ افزوده شده است. در این مطلب قصد داریم به معرفی این نوع فلیپ فلاپ و اصول کاری آن بپردازیم.

یکی از بزرگترین معایب مدارات بایاستابل (Bistable) گیت پایهای SR NAND این است که شرایط ورودی تعریف نشده SET=۰ و RESET=۰ ممنوع است. این شرایط منجر به این میشود که هر دو خروجی در سطح یک منطقی باشند و عمل لچ کردن (Latching) فیدبک را دو بار انجام دهد. هر کدام از ورودیها که اول به سطح منطقی یک برود، کنترل خود را از دست میدهد، در حالی که ورودی دیگر هنوز در سطح صفر منطقی است و کنترل حالت نهایی خروجی را در دست دارد.

به منظور جلوگیری از این اتفاق، یک معکوسکننده میتواند بین ورودیهای SET و RESET متصل شود و نوعی دیگر از فلیپ فلاپها را تولید کنند که با عناوین لچ داده (Data Latch)، فلیپ فلاپ تاخیری (Delay Flip Flop)، بایاستابل نوع D یا D-type Bistable و یا فلیپ فلاپ نوع D شناخته میشوند.

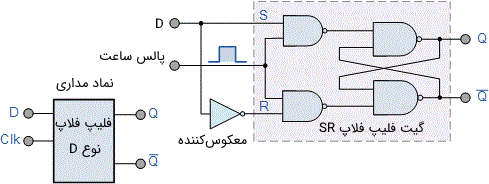

فلیپ فلاپ D، بدون شک یکی از مهمترین انواع فلیپ فلاپهای کلاکدار است؛ زیرا این فلیپ فلاپ اطمینان حاصل میکند که ورودیهای R و S به صورت همزمان با یکدیگر در سطح منطقی صفر نباشند. فلیپ فلاپ D، از یک فلیپ فلاپ RS ساخته شده است که یک معکوسکننده بین ورودیهای R و S افزوده شده است و داده ورودی تکی D مطابق شکل زیر به فلیپ فلاپ وارد میشود. این داده ورودی تکی که با عنوان D مشخص میشود، بدون تاخیر به ورودی SET فلیپ فلاپ اعمال میشود. همچنین معکوسشده ورودی D را به ورودی RESET فلیپ فلاپ وارد میکنند؛ بنابراین از یک فلیپ فلاپ حساس به سطح RS، یک فلیپ فلاپ حساس به سطح D ایجاد میشود که در آن S=D و R = NOT D است.

یکی از بزرگترین معایب مدارات بایاستابل (Bistable) گیت پایهای SR NAND این است که شرایط ورودی تعریف نشده SET=۰ و RESET=۰ ممنوع است. این شرایط منجر به این میشود که هر دو خروجی در سطح یک منطقی باشند و عمل لچ کردن (Latching) فیدبک را دو بار انجام دهد. هر کدام از ورودیها که اول به سطح منطقی یک برود، کنترل خود را از دست میدهد، در حالی که ورودی دیگر هنوز در سطح صفر منطقی است و کنترل حالت نهایی خروجی را در دست دارد.

به منظور جلوگیری از این اتفاق، یک معکوسکننده میتواند بین ورودیهای SET و RESET متصل شود و نوعی دیگر از فلیپ فلاپها را تولید کنند که با عناوین لچ داده (Data Latch)، فلیپ فلاپ تاخیری (Delay Flip Flop)، بایاستابل نوع D یا D-type Bistable و یا فلیپ فلاپ نوع D شناخته میشوند.

فلیپ فلاپ D، بدون شک یکی از مهمترین انواع فلیپ فلاپهای کلاکدار است؛ زیرا این فلیپ فلاپ اطمینان حاصل میکند که ورودیهای R و S به صورت همزمان با یکدیگر در سطح منطقی صفر نباشند. فلیپ فلاپ D، از یک فلیپ فلاپ RS ساخته شده است که یک معکوسکننده بین ورودیهای R و S افزوده شده است و داده ورودی تکی D مطابق شکل زیر به فلیپ فلاپ وارد میشود. این داده ورودی تکی که با عنوان D مشخص میشود، بدون تاخیر به ورودی SET فلیپ فلاپ اعمال میشود. همچنین معکوسشده ورودی D را به ورودی RESET فلیپ فلاپ وارد میکنند؛ بنابراین از یک فلیپ فلاپ حساس به سطح RS، یک فلیپ فلاپ حساس به سطح D ایجاد میشود که در آن S=D و R = NOT D است.

مدار فلیپ فلاپ نوع D

در یک فلیپ فلاپ نوع RS، دو ورودی وجود دارد. یکی از این ورودیها برای SET کردن خروجی و ورودی دیگر برای RESET کردن آن است. از طریق اتصال یک معکوسکننده (گیت NOT) به فلیپ فلاپ RS میتوانیم فلیپ فلاپ را با استفاده از فقط یک ورودی ست و ریست کنیم، در واقع در این نوع فلیپ فلاپ دو سیگنال ورودی مکمل یکدیگر شدهاند. مکمل بودن ورودیها منجر به جلوگیری از این خطای ذاتی موجود در لچهای RS میشود که در این لچها نباید دو ورودی همزمان در سطح LOW باشند (این حالت در فلیپ فلاپ SR ممکن نیست).

ورودی تکی، ورودی داده نام دارد. اگر ورودی داده در حالت HIGH نگه داشته شود، فلیپ فلاپ نوع D ست میشود و اگر این ورودی در حالت LOW باشد، خروجی تغییر حالت میدهد و ریست میشود. اگرچه این حالت معمولا بی معنی است؛ زیرا خروجی فلیپ فلاپ در هر پالس اعمالی به ورودی داده تغییر میکند.

برای خودداری از این عمل، یک ورودی اضافی دیگر نیز به فلیپ فلاپ افزوده شده است که ورودی کلاک یا فعالساز (Enable) نام دارد و دادههای ورودی را از مدار لچ فلیپ فلاپ (بعد از اینکه دادههای مطلوب ذخیره شدند) ایزوله میکند. تاثیر این ورودی در این است که وضعیت داده ورودی فقط در صورتی در خروجی Q کپی میشود که پالس ساعت یا کلاک فعال باشد؛ بنابراین پایه و اصول کار یک فلیپ فلاپ نوع D به این صورت شکل گرفته است.

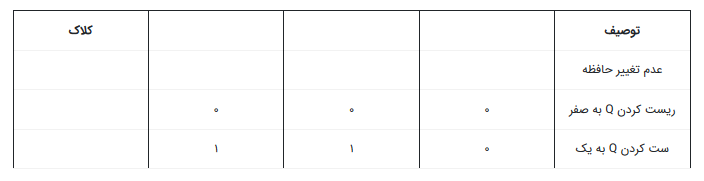

فلیپ فلاپ نوع D تا زمانی که پالس ساعت در سطح HIGH باشد، هر سطح منطقی که به ترمینال داده اعمال شود را در خروجی ظاهر کرده و ذخیرهسازی میکند. اگر پالس کلاک به سطح LOW برود، ورودیهای ست و ریست فلیپ فلاپ هر دو در سطح یک نگه داشته میشوند و در نتیجه خروجی فلیپ فلاپ تغییر نخواهد کرد و هر دادهای را که قبل از گذار حالت سیگنال کلاک در خروجی ظاهر شده بود را ذخیره میکند. به عبارت دیگر خروجی در سطح صفر یا سطح یک لچ میشود. جدول درستی فلیپ فلاپ نوع D در زیر آورده شده است.

توجه کنید که علامتهای و جهت پالس ساعت را نشان میدهند؛ زیرا فلیپ فلاپ نوع D حساس به لبه است و در لبهها تریگر میشود.

فلیپ فلاپ Master-Slave D

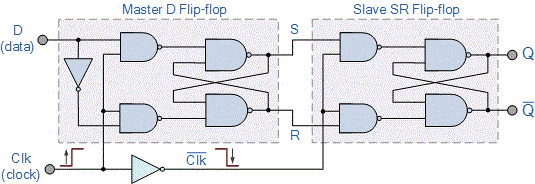

فلیپ فلاپ پایهای نوع D میتواند بیشتر نیز ارتقا داده شود و یک فلیپ فلاپ SR دومی نیز به خروجی آن اضافه شود که این فلیپ فلاپ با یک پالس کلاک مکمل فعالسازی میشود. این نوع از فلیپ فلاپهای نوع D را فلیپ فلاپ فرمانده-فرمانبر یا Master-Slave میگویند. در لبه بالا رونده (سطح LOW به سطح HIGH) پالس کلاک طبقه اول، فلیپ فلاپ Mater حالت ورودی را به D لچ میکند، در حالیکه حالت خروجی غیرفعال است.

فلیپ فلاپ Master-Slave D

در لبه پایین رونده (سطح HIGH به سطح LOW) پالس کلاک مربوط به طبقه دوم که Slave نام دارد، فعال میشود و به مقدار خروجی از طبقه قبل از خود یا طبقه Master لچ میشود؛ بنابراین مشخص است که در لبههای منفی پالس کلاک، حالت خروجی تریگر میشود. فلیپ فلاپ Master-Slave را میتوان از طریق اتصال آبشاری دو لچ ساخت که با پالس کلاکهای در فاز مخالف تغذیه میشوند.

از شکل بالا میتوان دریافت که در لبه بالا رونده سیگنال پالس کلاک، فلیپ فلاپ Master دادهها را از ورودی داده D بارگذاری میکند، بنابراین فلیپ فلاپ Master روشن است. اما در لبه پایین رونده پالس کلاک، فلیپ فلاپ Slave داده را بارگذاری میکند، پس این بار فلیپ فلاپ Slave روشن است. بنابراین، در هر لحظه یکی از فلیپ فلاپهای Master یا Slave روشن و دیگری خاموش است، اما هر دو همزمان نمیتوانند روشن باشند. پس زمانی که یک پالس کامل ۰-۱-۰ به ورودی کلاک اعمال شود، خروجی Q مقدار D را در خود کپی میکند.

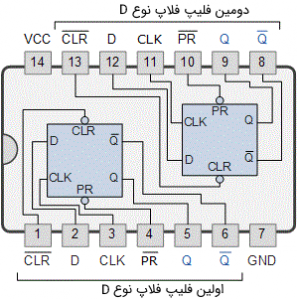

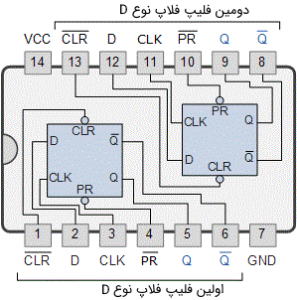

آیسیهای مختلفی برای فلیپ فلاپ D، هم از نوع TTL و هم CMOS وجود دارند که متداولترین آن ۷۴LS۷۴ (یک آیسی فلیپ فلاپ D دوتایی) است. این آیسی شامل دو فلیپ فلاپ بایاستابل D در یک چیپ است و امکان ایجاد فلیپ فلاپ تکی یا Master-Slave را فراهم میکند. آیسی دیگر فلیپ فلاپهای نوع D، آیسی ۷۴LS۱۷۴ HEX است که دارای ورودی مستقیم CLEAR است. آیسی ۷۴LS۱۷۵ Quad دارای خروجی مکمل بوده و ۷۴LS۲۷۳ Octal دارای هشت عدد فلیپ فلاپ D با یک ورودی CLEAR در یک پکیج است. نمایی از مدار داخلی آیسی ۷۴LS۷۴ Dual در شکل زیر دیده میشود.

مدار داخلی آیسی ۷۴LS۷۴ Dual

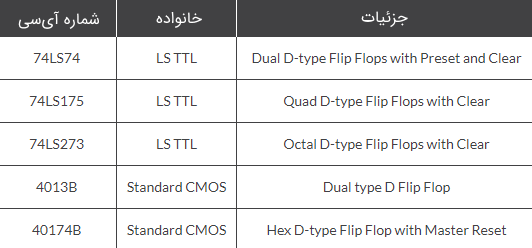

در تصویر زیر تعدادی از آیسیهای فلیپ فلاپ نوع D را میتوان دید.

انواع آیسیهای فلیپ فلاپ نوع D

استفاده از فلیپ فلاپ نوع D در مقسمهای فرکانسی

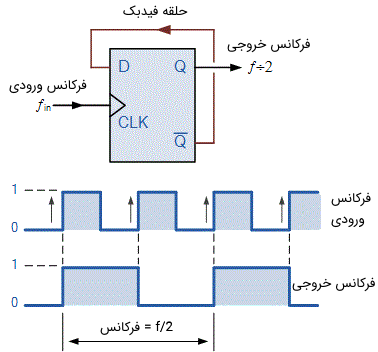

یکی از مهمترین کاربردهای فلیپ فلاپهای نوع D در مقسمهای فرکانسی است. اگر خروجی در یک فلیپ فلاپ D مستقیما به ورودی D آن متصل شود، منجر به ایجاد یک فیدبک حلقه بسته در فلیپ فلاپ میشود و در نتیجه پالس کلاکهای متوالی (یک بار از هر دو پالس کلاک) تغییر وضعیت یا تاگل بایاستابل ایجاد میکنند. در مطلب مقسمهای فرکانسی کامل به این مطلب پرداخته میشود که چگونه با استفاده از یک لچ داده یا فلیپ فلاپ D مقسمهای باینری یا مقسمهای فرکانسی ایجاد کرد. این مقسمهای فرکانسی در تولید مدارات شمارنده مقسم بر دو کاربرد دارند. در این شمارندهها، فرکانس پالس خروجی دقیقا نصف فرکانس پالس اعمالی به کلاک ورودی است؛ بنابراین از طریق قرار دادن یک حلقه فیدبک در فلیپ فلاپ نوع D، نوع دیگری از فلیپ فلاپها که به فلیپ فلاپهای نوع T مشهور هستند، ایجاد میشوند. فلیپ فلاپهای نوع T میتوانند در مدارات مقسم بر دو و شمارندههای باینری مانند شکل زیر مورد استفاده قرار گیرند.

مقسم فرکانسی با استفاده از فلیپ فلاپ نوع D

از شکل موج داده شده در بالا میتوان به این نکته پی برد که با ایجاد فیدبک از خروجی به ترمینال ورودی D، پالس خروجی از Q دارای فرکانسی دقیقا برابر با نصف فرکانس کلاک ورودی خواهد بود. به عبارت دیگر، مدار سبب ایجاد تقسیم فرکانسی میشود که در این حالت فرکانس کلاک ورودی بر فاکتور دو تقسیم میشود، بنابراین از هر دو تناوب پالس کلاک، یک بار خروجی Q یک میشود.

فلیپ فلاپ D به عنوان لچ داده

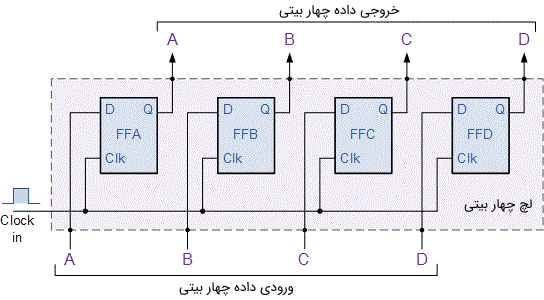

علاوه بر مقسم فرکانسی، کاربرد مفید دیگر فلیپ فلاپ D به عنوان لچ یا نگهدار داده است. یک لچ داده میتواند به عنوان قطعهای استفاده شود که دادهها را نگه میدارد و مقادیر حاضر در ورودی خود را به یاد میسپارد؛ بنابراین فلیپ فلاپهای D تا حدودی شبیه به ادوات حافظه تک بیتی و آیسیهایی مانند TTL ۷۴LS۷۴ یا CMOS ۴۰۴۲ عمل میکنند که به فرم دو تایی و دقیقا برای این هدف ساخته شدهاند. از طریق اتصال ۴ لچ یک بیتی به یکدیگر، به گونهای که تمام ورودیهای کلاک آنها به یکدیگر متصل شده باشد، یک لچ داده چهار بیتی ساده مانند شکل زیر ایجاد میشود.

لچ داده چهار بیتی

لچ داده شفاف

لچهای داده در الکترونیک و مدارات کامپیوتری جزو ادوات بسیار مفید هستند. این ادوات میتوانند برای داشتن امپدانس خروجی بسیار بالا، هم در خروجی Q و هم در خروجی مکمل یا معکوس، طراحی شوند تا زمانی که به عنوان بافر، پورت I/O، درایور خط دو جهته (Bi-Directional Bus Driver) و یا حتی درایور نمایشگرها مورد استفاده قرار میگیرند، اثر امپدانس را روی مدار متصل کاهش دهند.

اما یک لچ داده یک بیتی، به تنهایی کاربردی نیست و در عوض آیسیهای تجاری موجود تعداد ۴، ۸، ۱۰، ۱۶ و حتی ۳۲ لچ داده تکی را در یک پکیج آیسی فراهم میآورند. ۷۴LS۳۷۳ Octal، یک نمونه از چنین آیسیهایی است که به آیسی Transparent Latch مشهور است. این آیسی که از هشت لچ داده تکی تشکیل شده است، به این دلیل Transparent نام دارد که اگر پالس کلاک در سطح یک منطقی یا HIGH باشد، خروجیها در Q دقیقا مقدار ورودیها در D را دنبال میکنند. در این پیکربندی، گفته میشود که لچ باز است و مسیر از ورودی به خروجی شفاف (Transparent) است؛ زیرا دادهها بدون محدودیت از آن عبور میکنند.

زمانی که سیگنال کلاک ورودی در سطح LOW یا صفر منطقی باشد، لچ بسته است و خروجی در مقدار آخرین دادهای که قبل از تغییر وضعیت کلاک در خروجی ظاهر شده بود، لچ میشود و در پاسخ به دیگر تغییر نخواهد کرد. نمایی از این لچ داده در شکل زیر نشان داده شده است.

لچ داده Tranparent هشت بیتی

خلاصه

فلیپ فلاپ D با استفاده از دو فلیپ فلاپ SR ساخته میشود که پشت به پشت یکدیگر بسته شدهاند. در این فلیپ فلاپ یک گیت معکوسکننده (گیت NOT) بین دو ورودی S و R متصل میشود که امکان ورود سیگنال داده D را فراهم میکند. مدار فلیپ فلاپ پایه D را میتوان با اضافه کردن فلیپ فلاپ دوم به خروجی فلیپ فلاپ اول ارتقا داد که فلیپ فلاپ دوم توسط متمم پالس کلاک فعال میشود. این نوع فلیپ فلاپ را Master-Slave مینامند.

تفاوت بین یک لچ D و یک فلیپ فلاپ نوع D در این است که، لچ فاقد سیگنال کلاک برای تغییر وضعیت است، اما فلیپ فلاپ با استفاده از کلاک وضعیت خود را تغییر میدهد. فلیپ فلاپ D یک وسیله حساس به لبه است که دادههای ورودی را در هر لبه بالا رونده یا پایین رونده سیگنال کلاک به خروجی منتقل میکند. اما لچهای داده، مانند لچهای D و لچهای شفاف وسایل حساس به سطح هستند.

لینک کوتاه

از ارسال دیدگاه های نا مرتبط با متن خبر، تکرار نظر دیگران، توهین به سایر کاربران و ارسال متن های طولانی خودداری نمایید.

لطفا نظرات بدون بی احترامی، افترا و توهین به مسئولان، اقلیت ها، قومیت ها و ... باشد و به طور کلی مغایرتی با اصول اخلاقی و قوانین کشور نداشته باشد.

در غیر این صورت، «برق نیوز» مطلب مورد نظر را رد یا بنا به تشخیص خود با ممیزی منتشر خواهد کرد.